One-to-Five LVPECL/LVCMOS Output Clock and Data Driver

Analog Devices

RSS

Sample

RSS

Sample

- Darmowa próbka

- MPN:

- MAX9324

- Producent:

- ANALOG DEVICES

- Dodany do bazy:

- Ostatnio widziany:

Sugerowane produkty dla onetofive

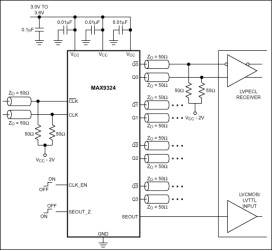

The MAX9324 low-skew, low-jitter, clock and data driver distributes a differential LVPECL input to four differential LVPECL outputs and one single-ended LVCMOS output. All outputs default to logic low when the differential inputs equal GND or are left open. The MAX9324 operates from 3.0V to 3.6V, making it ideal for 3.3V systems, and consumes only 25mA (max) of supply current.

The MAX9324 features low 150ps (max) part-to-part skew, low 15ps output-to-output skew, and low 1.7ps RMS jitter, making the device ideal for clock and data distribution across a backplane or board. CLKEN and SEOUTZ control the status of the various outputs. Asserting CLKEN low configures the differential (Q, Q) outputs to a differential low condition and SEOUT to a single-ended logic-low state. CLKEN operation is synchronous with the CLK inputs. A logic high on SEOUTZ places SEOUT in a high-impedance state. SEOUTZ is asynchronous with the CLK (active-low CLK) inputs.

The MAX9324 is available in space-saving 20-pin TSSOP and ultra-small 20-pin 4mm x 4mm thin QFN packages and operates over the extended (-40°C to +85°C) temperature range.

Applications

* Automated Test Equipment (ATE) * Central Office Backplane Clock Distribution * Data and Clock Driver and Buffer * DSLAM Backplane * Low-Jitter Data Repeater * Precision Clock Distribution * Wireless Base Stations

* Differential Output-to-Output Skew

* 1.7psRMS Added Random Jitter

* 150ps (max) Part-to-Part Skew

* 450ps Propagation Delay

* Synchronous Output Enable/Disable

* Single-Ended Monitor Output

* Outputs Assert Low when CLK, active-low CLK are Open or at GND

* 3.0V to 3.6V Supply Voltage Range

* -40°C to +85°C Operating Temperature Range

Elecena nie prowadzi sprzedaży elementów elektronicznych, ani w niej nie pośredniczy.

Produkt pochodzi z oferty sklepu Analog Devices