14-Bit, 170 MSPS/250 MSPS, JESD204B, Analog-to-Digital Converter

Analog Devices

RSS

Sample

RSS

Sample

- Darmowa próbka

- MPN:

- AD9683

- Producent:

- ANALOG DEVICES

- Dodany do bazy:

- Ostatnio widziany:

- Zmiana ceny:

- -100% (17.01.2025)

- Poprzednia cena:

- 49.31

Sugerowane produkty dla ad9683

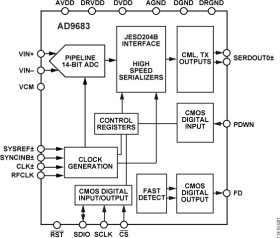

The AD9683 is a 14-bit ADC with sampling speeds of up to 250 MSPS. The AD9683 supports communications applications where low cost, small size, wide bandwidth, and versatility are desired. The ADC core features a multistage, differential pipelined architecture with integrated output error correction logic. The ADC core features wide bandwidth inputs supporting a variety of user-selectable input ranges. An integrated voltage reference eases design considerations. A duty cycle stabilizer (DCS) is provided to compensate for variations in the ADC clock duty cycle, allowing the converter to maintain excellent performance. The JESD204B high speed serial interface reduces board routing requirements and lowers pin count requirements for the receiving device. The ADC output data is routed directly to the JESD204B serial output lane. These outputs are at CML voltage levels. Data can be sent through the lane at the maximum sampling rate of 250 MSPS, which results in a lane rate of 5 Gbps. Synchronization inputs (SYNCINB± and SYSREF±) are provided. Flexible power-down options allow significant power savings, when desired. Programmable overrange level detection is supported via the dedicated fast detect pins. Programming for setup and control is accomplished using a 3-wire SPI-compatible serial interface. The AD9683 is available in a 32-lead LFCSP and is specified over the industrial temperature range of −40°C to +85°C.

Product Highlights

* Integrated 14-bit, 170 MSPS/250 MSPS ADC.

* The configurable JESD204B output block supports lane

rates up to 5 Gbps.

* An on-chip, phase-locked loop (PLL) allows users to provide a

single ADC sampling clock; the PLL multiplies the ADC

sampling clock to produce the corresponding JESD204B

data rate clock.

* Support for an optional radio frequency (RF) clock input to

ease system board design.

* Proprietary differential input maintains excellent SNR

performance for input frequencies of up to 400 MHz.

* Operation from a single 1.8 V power supply.

* Standard serial port interface (SPI) that supports various

product features and functions, such as controlling the clock

DCS, power-down, test modes, voltage reference mode,

overrange fast detection, and serial output configuration.

Applications

* Communications

* Diversity radio systems

* Multimode digital receivers (3G)

TD-SCDMA, WiMAX, W-CDMA, CDMA2000, GSM, EDGE, LTE

* DOCSIS 3.0 CMTS upstream receive paths

* HFC digital reverse path receivers

* Smart antenna systems

* Electronic test and measurement equipment

* Radar receivers

* COMSEC radio architectures

* IED detection/jamming systems

* General-purpose software radios

* Broadband data applications

* Ultrasound equipment

* JESD204B Subclass 0 or Subclass 1 coded serial digital outputs

* Signal-to-noise ratio (SNR) = 70.6 dBFS at 185 MHz AIN and 250 MSPS

* Spurious-free dynamic range (SFDR) = 88 dBc at 185 MHz AIN and 250 MSPS

* Total power consumption: 434 mW at 250 MSPS

* 1.8 V supply voltages

* Integer 1-to-8 input clock divider

* Sample rates of up to 250 MSPS

* Intermediate frequency (IF) sampling frequencies of up to 400 MHz

* Internal analog-to-digital converter (ADC) voltage reference

* Flexible analog input range: 1.4 V p-p to 2.0 V p-p (1.75 V p-p nominal)

* ADC clock duty cycle stabilizer (DCS)

* Serial port control

* Energy saving power-down modes

Elecena nie prowadzi sprzedaży elementów elektronicznych, ani w niej nie pośredniczy.

Produkt pochodzi z oferty sklepu Analog Devices