Ultralow Jitter, 4.5GHz PLL with 11 Outputs and JESD204B / JESD204C Support

Analog Devices

RSS

Sample

RSS

Sample

- Darmowa próbka

- MPN:

- LTC6952

- Producent:

- ANALOG DEVICES

- Dodany do bazy:

- Ostatnio widziany:

- Zmiana ceny:

- -100% (22.01.2025)

- Poprzednia cena:

- 19.54

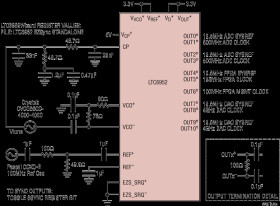

The LTC6952 is a high performance, ultralow jitter, JESD204B/C clock generation and distribution IC. It includes a Phase Locked Loop (PLL) core, consisting of a reference divider, phase-frequency detector (PFD) with a phase-lock indicator, ultralow noise charge pump and integer feedback divider. The LTC6952’s eleven outputs can be configured as up to five JESD204B/C subclass 1 device clock/SYSREF pairs plus one general purpose output, or simply eleven general purpose clock outputs for non-JESD204B/C applications. Each output has its own individually programmable frequency divider and output driver. All outputs can also be synchronized and set to precise phase alignment using individual coarse half-cycle digital delays and fine analog time delays.

For applications requiring more than eleven total outputs, multiple LTC6952s can be connected together using the EZSync or ParallelSync synchronization protocols.

Applications

* High Performance Data Converter Clocking

* Wireless Infrastructure

* Test and Measurement

* JESD204B/C, Subclass 1 SYSREF Signal Generation

* Low Noise Integer-N PLL

* Additive Output Jitter < 6fsRMS

* (Integration BW = 12kHz to 20MHz, f = 4.5GHz)

* Additive Output Jitter 65fsRMS (ADC SNR Method)

* EZSync™, ParallelSync™ Multichip Synchronization

* –229dBc/Hz Normalized In-Band Phase Noise Floor

* –281dBc/Hz Normalized In-Band 1/f Noise

Elecena nie prowadzi sprzedaży elementów elektronicznych, ani w niej nie pośredniczy.

Produkt pochodzi z oferty sklepu Analog Devices