300 MHz TigerSHARC Processor with 6 Mbit on-chip SRAM

Analog Devices

RSS

Sample

RSS

Sample

- Darmowa próbka

- MPN:

- ADSP-TS101S

- Producent:

- ANALOG DEVICES

- Dodany do bazy:

- Ostatnio widziany:

Sugerowane produkty dla or600

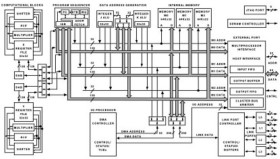

The ADSP-TS101S TigerSHARC® processor is an ultrahigh performance, Static Superscalar™ processor optimized for large signal processing tasks and communications infrastructure. The DSP combines very wide memory widths with dual computation blocks—supporting 32- and 40-bit floating-point and 8-, 16-, 32-, and 64-bit fixed-point processing—to set a new standard of performance for digital signal processors. The TigerSHARC processor’s Static Superscalar architecture lets the processor execute up to four instructions each cycle, performing 24 fixed-point (16-bit) operations or six floating-point operations.

Three independent 128-bit-wide internal data buses, each connecting to one of the three 2M bit memory banks, enable quad word data, instruction, and I/O accesses and provide 14.4G bytes per second of internal memory bandwidth. Operating at 300 MHz, the ADSP-TS101S processor’s core has a 3.3 ns instruction cycle time. Using its single-instruction, multiple-data (SIMD) features, the ADSP-TS101S can perform 2.4 billion 40-bit MACs or 600 million 80-bit MACs per second. Table 1 and Table 2 in the data sheet show the DSP’s performance benchmarks.

* 300 MHz, 3.3 ns instruction cycle rate

* 6M bits of internal—on-chip—SRAM memory

* 19 mm × 19 mm (484-ball) CSPBGA or 27 mm× 27 mm (625-ball) PBGA package

* Dual computation blocks—each containing an ALU, a multiplier, a shifter, and a register file

* Dual integer ALUs, providing data addressing and pointer manipulation

* Integrated I/O includes 14-channel DMA controller, external port, 4 link ports, SDRAM controller, programmable flag pins, 2 timers, and timer expired pin for system integration

* 1149.1 IEEE compliant JTAG test access port for on-chip emulation

* On-chip arbitration for glueless multiprocessing with up to 8 TigerSHARC processors on a bus

Elecena nie prowadzi sprzedaży elementów elektronicznych, ani w niej nie pośredniczy.

Produkt pochodzi z oferty sklepu Analog Devices