Dual DPLL Digitized Clock Synchronizer

Analog Devices

RSS

Sample

RSS

Sample

- Darmowa próbka

- MPN:

- AD9546

- Producent:

- ANALOG DEVICES

- Dodany do bazy:

- Ostatnio widziany:

- Zmiana ceny:

- -100% (17.01.2025)

- Poprzednia cena:

- 19.25

Sugerowane produkty dla ad9546

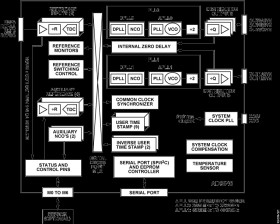

The AD9546 incorporates digitized clocking technology that efficiently transports and distributes clock signals in systems. Digitized clocking allows the design of flexible and scalable clock transport systems with well controlled phase (time) alignment. These characteristics make the AD9546 a leading choice for the design of network equipment that must meet the synchronization requirements for IEEE® 1588™ boundary clocks per ITU-T G.8273.2 Class D. Digitized clocking is also relevant in applications requiring the accurate transport of frequency and phase to multiple usage endpoints (for example, distributing synchronized system reference (SYSREF) clocks to an array of ADC channels).

The AD9546 supports existing and emerging International Telecommunications Union (ITU) standards for the delivery of frequency, phase, and time of day over service provider packet networks (ITU-T G.8262, ITU-T G.812, ITU-T G.813, ITU-T G.823, ITU-T G.824, ITU-T G.825, and ITU-T G.8273.2).

The 10 clock outputs of the AD9546 synchronize to any one of up to eight input references. The digital phase-locked loops (DPLLs) reduce timing jitter associated with the external references, and the analog phase-locked loops (APLLs) provide frequency translation with low jitter output clocks. The digitally controlled loop and holdover circuitry continuously generate a low jitter output signal, even when all reference inputs fail.

The AD9546 is available in a 48-lead LFCSP (7 mm × 7 mm) package and operates over the −40°C to +85°C temperature range.

Throughout this data sheet, a single function of a multifunction pin name may be referenced when only that function is relevant (for example, M5 for SDO/M5).

APPLICATIONS

* 5G timing transport high precision synchronization

* Global positioning system (GPS), precision time protocol (PTP) (IEEE 1588), and synchronous Ethernet (SyncE) jitter cleanup and synchronization

* Optical transport networks (OTN), synchronous digital hierarchy (SDH), and macro and small cell base stations Small base station clocking (baseband and radio)

* Stratum 2, Stratum 3e, and Stratum 3 holdover, jitter cleanup, and phase transient control

* JESD204B support for analog-to-digital converter (ADC) and digital-to-analog converter (DAC) clocking

* Carrier Ethernet

* Digitized clock transport subsystem* 9 independent UTS blocks (time stamp egress ports)* 2 independent IUTS blocks (time stamp ingress ports)* Dual DPLL synchronizes 1 Hz to 750 MHz physical layer clocks, providing frequency translation with jitter cleaning of noisy references* Complies with ITU-T G.8262 and Telcordia GR-253* Supports Telcordia GR-1244, ITU-T G.812, ITU-T G.813, ITU-T G.823, ITU-T G.824, ITU-T G.825, and ITU-T G.8273.2* Continuous frequency monitoring and reference validation for frequency deviation as low as 50 ppb (5 × 10−8)* Both DPLLs feature a 24-bit fractional divider with 24-bit programmable modulus* Programmable digital loop filter bandwidth: 0.0001 Hz to 1850 Hz* 2 independent, programmable auxiliary NCOs (1 Hz to 65,535 Hz, resolution < 1.37 pHz), suitable for IEEE 1588 Version 2 servo feedback in PTP applications* Automatic and manual holdover and reference switchover, providing zero delay, hitless, or phase buildout operation

Elecena nie prowadzi sprzedaży elementów elektronicznych, ani w niej nie pośredniczy.

Produkt pochodzi z oferty sklepu Analog Devices