16-Channel, 125 MHz Bandwidth, JESD204B Analog-to-Digital Converter

Analog Devices

RSS

Sample

RSS

Sample

- Darmowa próbka

- MPN:

- AD9083

- Producent:

- ANALOG DEVICES

- Dodany do bazy:

- Ostatnio widziany:

- Zmiana ceny:

- -100% (20.01.2025)

- Poprzednia cena:

- 326.33

Sugerowane produkty dla ad9083

The AD9083 is a 16-channel, 125 MHz bandwidth, continuous time Σ-Δ (CTSD) ADC. The device features an on-chip, programmable, single-pole antialiasing filter and termination resistor that is designed for low power, small size, and ease of use.

The 16 ADC cores features a first-order, CTSD modulator architecture with integrated, background nonlinearity correction logic and self cancelling dither. Each ADC features wide bandwidth inputs supporting a variety of user-selectable input ranges. An integrated voltage reference eases design considerations.

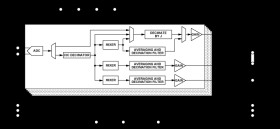

The analog input and clock signals are differential inputs. Each ADC has a signal processing tile to filter out of band shaped noise from the Σ-Δ ADC and reduce the sample rate. Each tile contains a cascaded integrator comb (CIC) filter, a quadrature digital downconverter (DDC) with multiple finite input response (FIR) decimation filters (decimate by J block), or up to three quadrature DDC channels with averaging decimation filters for data gating applications.

Users can configure the Subclass 1 JESD204B based, high speed serialized output in a variety of lane configurations (up to four), depending on the DDC configuration and the acceptable lane rate of the receiving logic device. Multiple device synchronization is supported through the SYSREF±, TRIG±, and SYNCINB± input pins.

The AD9083 has flexible power-down options that allow significant power savings when desired. All of these features can be programmed using a 1.8 V capable 3-wire serial port interface (SPI).

The AD9083 is available in a Pb-free, 100-ball CSPBGA and is specified over the −40°C to +85°C industrial temperature range.

This product is protected by a US patent.

APPLICATIONS

* Millimeter wave imaging

* Electronic beam forming and phased arrays

* Multichannel wideband receivers

* Electronic support measures

PRODUCT HIGHLIGHTS

* Continuous time, Σ-Δ analog-to-digital converters (ADCs) support signal bandwidths of up to 125 MHz with low power and minimal filtering.

* Integrated digital processing blocks reduce data payload and lower overall system cost.

* Configurable JESD204B interface reduces printed circuit board (PCB) complexity.

* Flexible power-down options.

* SPI interface controls various product features and functions to meet specific system requirements.

* Small, 9 mm × 9 mm, 100-ball CSPBGA package, simple interface, and integrated digital processing save PCB space.

* 1.0 V and 1.8 V supply operation

* 125 MHz usable analog input bandwidth

* Sample rate up to 2 GSPS

* Noise spectral density in 100 MHz bandwidth = −145 dBFS/Hz, 2.0 GSPS encode

* SNR = 66 dBFS in 100 MHz bandwidth, 2.0 GSPS encode

* SNR = 82 dBFS in 15.625 MHz bandwidth, 2.0 GSPS encode

* SFDR = 60 dBc in 100 MHz bandwidth, 2.0 GSPS encode

* SFDR = 80 dBc in 15.625 MHz bandwidth, 2.0 GSPS encode

* Large signal dither

Elecena nie prowadzi sprzedaży elementów elektronicznych, ani w niej nie pośredniczy.

Produkt pochodzi z oferty sklepu Analog Devices