Quad Input, 10-Output, Dual DPLL, 1 pps Synchronizer and Jitter Cleaner

Analog Devices

RSS

Sample

RSS

Sample

- Darmowa próbka

- MPN:

- AD9544

- Producent:

- ANALOG DEVICES

- Dodany do bazy:

- Ostatnio widziany:

- Zmiana ceny:

- -100% (22.01.2025)

- Poprzednia cena:

- 13.46

Sugerowane produkty dla ad9544

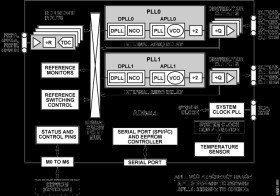

The 10 clock outputs of the AD9544 are synchronized to any one of up to four input references. The digital phase-locked loops (DPLLs) reduce timing jitter associated with the external references. The digitally controlled loop and holdover circuitry continuously generate a low jitter output signal, even when all reference inputs fail.

The AD9544 is available in a 48-lead LFCSP (7 mm × 7 mm) package and operates over the −40°C to +85°C temperature range.

Note that throughout this data sheet, multifunction pins, such as SDO/M5, are referred to either by the entire pin name or by a single function of the pin, for example, M5, when only that function is relevant.

Appliations

* SyncE and GPS synchronization and jitter cleanup

* Optical transport networks (OTN), SDH, and macro and small cell base stations

* OTN mapping/demapping with jitter cleaning

* Small base station clocking, including baseband and radio

* Stratum 2, Stratum 3e, and Stratum 3 holdover, jitter cleanup, and phase transient control

* JESD204B support for analog-to-digital converter (ADC) and digital-to-analog converter (DAC) clocking

* Cable infrastructures

* Carrier Ethernet

* Dual DPLL synchronizes 1 Hz to 750 MHz physical layer clocks providing frequency translation with jitter cleaning of noisy references

* Complies with ITU-T G.8262 and Telcordia GR-253

* Supports Telcordia GR-1244, ITU-T G.812, G.813, G.823, G.824, and G.825

* Continuous frequency monitoring and reference validation for frequency deviation as low as 50 ppb

* Both DPLLs feature a 24-bit fractional divider with 24-bit programmable modulus

* Programmable digital loop filter bandwidth: 10−4 Hz to 1850 Hz

* Automatic and manual holdover and reference switchover, providing zero delay, hitless, or phase buildout operation

* Programmable priority-based reference switching with manual, automatic revertive, and automatic nonrevertive modes supported

* 5 pairs of clock output pins with each pair useable as differential LVDS/HCSL/CML or as 2 single-ended outputs (1 Hz to 500 MHz)

* 2 differential or 4 single-ended input references

* Crosspoint mux interconnects reference inputs to PLLs

* Supports embedded (modulated) input/output clock signals

* Fast DPLL locking modes

* Provides internal capability to combine the low phase noise of a crystal resonator or crystal oscillator with the frequency stability and accuracy of a TCXO or OCXO

* External EEPROM support for autonomous initialization

* Single 1.8 V power supply operation with internal regulation

* Built in temperature monitor/alarm and temperature compensation for enhanced zero delay performance

Elecena nie prowadzi sprzedaży elementów elektronicznych, ani w niej nie pośredniczy.

Produkt pochodzi z oferty sklepu Analog Devices