Single/Dual/Triple/Quad ATM/Packet PHYs with Built-In LIU

Analog Devices

RSS

Sample

RSS

Sample

- Darmowa próbka

- MPN:

- DS3182

- Producent:

- ANALOG DEVICES

- Dodany do bazy:

- Ostatnio widziany:

Sugerowane produkty dla ds3181

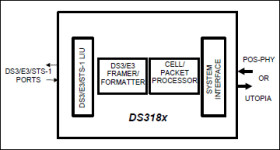

The DS3181, DS3182, DS3183, and DS3184 (DS318x) integrate ATM cell/HDLC packet processor(s) with a DS3/E3 framer(s) and LIU(s) to map/demap ATM cells or packets into as many as four DS3/E3 physical copper lines with DS3-framed, E3-framed, or clear-channel data streams on per-port basis.

Applications

* Access Concentrators * ATM and Frame Relay Equipment * Digital Cross Connect * Integrated Access Device (IAD) * Multiservice Access Platform (MSAP) * Multiservice Protocol Platform (MSPP) * PBXs * PDH Multiplexer/Demultiplexer * Routers and Switches * SONET/SDH ADM * SONET/SDH Muxes * Test Equipment

* Single (DS3181), Dual (DS3182), Triple (DS3183), or Quad (DS3184) with Integrated LIUATM/Packet PHYs for DS3, E3, and Clear-Channel 52Mbps (CC52)

* Pin Compatible for Ease of Port Density Migration in the Same PC Board Platform

* Each Port Independently Configurable

* Perform Receive Clock/Data Recovery and Transmit Waveshaping

* Jitter Attenuator can be Placed Either in the Receive or Transmit Paths

* Interfaces to 75Ω Coaxial Cable at Lengths Up 380 Meters or 1246 Feet (DS3) or 440 Meters or 1443 Feet (E3)

* Uses 1:2 Transformers on Both Tx and Rx

* Universal PHYs Map ATM Cells and/or HDLC Packets into DS3 or E3 Data Streams

* UTOPIA L2/L3 or POS-PHY L2/L3 or SPI-3 Interface with 8-, 16-, or 32-Bit Bus Width

* 66MHz UTOPIA L3 and POS-PHY L3 Clock

* 52MHz UTOPIA L2 and POS-PHY L2 Clock

* Ports Independently Configurable for Cell or Packet Traffic in POS-PHY Bus Modes

* Direct, PLCP, DSS, and Clear-Channel Cell Mapping

Elecena nie prowadzi sprzedaży elementów elektronicznych, ani w niej nie pośredniczy.

Produkt pochodzi z oferty sklepu Analog Devices