3.3V, 2.5Gbps/2.7Gbps, SDH/SONET 4:1 Serializer with Clock Synthesis

Analog Devices

RSS

Sample

RSS

Sample

- Darmowa próbka

- MPN:

- MAX3892

- Producent:

- ANALOG DEVICES

- Dodany do bazy:

- Ostatnio widziany:

Sugerowane produkty dla max3892

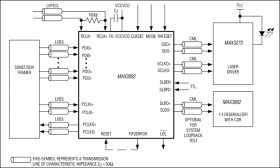

The MAX3892 serializer is ideal for converting 4-bit-wide, 622Mbps parallel data to 2.5Gbps serial data in DWDM and SONET/SDH applications. A 4 x 4-bit FIFO allows for any static delay between the parallel output clock and parallel input clock. Delay variation up to a unit interval (UI) is allowed after reset. A fully integrated phase-locked loop (PLL) synthesizes an internal 2.5GHz serial clock from a 622MHz, 155.5MHz, 77.8MHz, or 38.9MHz reference clock. A selectable dual VCO allows excellent jitter performance at both SONET and forward-error correction (FEC) data rates.

Operating from a single 3.3V supply, this device accepts low-voltage differential-signal (LVDS) clock and data inputs for interfacing with high-speed digital circuitry, and delivers current-mode logic (CML) serial data and clock outputs. A loopback data output is provided to facilitate system diagnostic testing. The MAX3892 is available in the extended temperature range (-40°C to +85°C) in 44-pin QFN and TQFN packages.

Applications

* Add/Drop Multiplexers * Backplane Interconnect * Dense Digital Cross-Connects * SONET/SDH OC-48 Transmission Systems * WDM Transponders

* Single +3.3V Supply

* 455mW Power Consumption

* 1.4psRMS Maximum Jitter Generation

* 4 x 4-Bit FIFO Input Buffer

* 622Mbps/666Mbps Parallel to 2.5Gbps/2.7Gbps Serial Conversion

* 622MHz/667MHz or 311MHz/333MHz Clock Input

* On-Chip Clock Synthesizer

* Multiple Clock Reference Frequencies:

* (622.08MHz, 155.52MHz, 77.76MHz, 38.88MHz) or (666.51MHz, 166.63MHz, 83.31MHz, 41.66MHz)

* LVDS Parallel Clock and Data Inputs

* CML Serial Data and Clock Outputs

* Additional CML Output for System Loopback Testing

Elecena nie prowadzi sprzedaży elementów elektronicznych, ani w niej nie pośredniczy.

Produkt pochodzi z oferty sklepu Analog Devices